电子元器件的失效分析借助各种测试技术和分析方法明确元器件的失效过程,分辨失效模式或机理,确定其最终的失效原因。肖特基二极管具有开关频率高和正向压降低等优点,但其反向击穿电压比较低,大多不高于60V,最高仅约100V,以致于限制了其应用范围。肖特基二极管以其较低的正向导通电压,更好的高频特性,在高速集成电路、微波技术等许多领域得到广泛应用。

肖特基二极管是利用金属与半导体接触形成的势垒而制成的二极管,它不同于扩散型PN结二极管,其正向压降只有PN结的一半,所以功耗可以降低一半。肖特基二极管利用一种多数载流子器件,不存在PN结二极管势垒少子注入和储存的瞬态恢复特性,这使得在相同的应用情况下,两者的恢复特性存在明显的差别,恢复时间大约为1:50,由于SBD的恢复时间要短的多,因此其开关速度比PN结二极管要快一倍,二极管的恢复时间越短,它的平均功率损耗就越小。

常规肖特基二极管对ESD并不敏感,其使用中的主要失效模式常为正向过流烧毁或反向过压击穿;但高耐压肖特基整流管由于其结构的特殊性,抗静电能力较常规肖特基二极管弱,在使用中仍要高度注意防静电问题,本文从实际失效案例说明肖特基功率整流管受静电损伤的机理,对高耐压肖特基整流管静电敏感度低的原因进行研究,并提出在生产、使用以及失效分析阶段的注意事项。

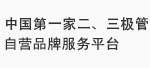

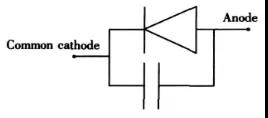

某电源模块输出整流二极管短路,该整流二极管为高效肖特基整流管,内部由2个共阴极的肖特基二极管组成,内部原理图见图1。

图1 器件内部原理示意图

1. 试验过程与结果

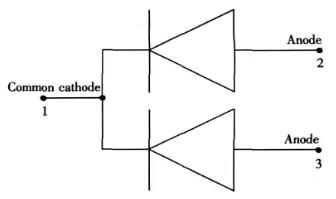

检查器件外观,未见有导致器件失效的异常状况,失效器件外观见图2。

图2 失效器件外观

用图示仪测试发现其中一个二极管正负极短路,用万用表测试正反向电阻均为1.4Ω。对器件进行颗粒碰撞噪声检测(PIND),没有发现器件内部可动多余物,排除可动金属多余物导致器件短路的可能性。

为判断外界气氛对器件性能的影响,对器件进行密封性检查,器件精粗检漏结果均合格。对失效器件进行内部气氛分析,发现器件密封腔体内并不含O。

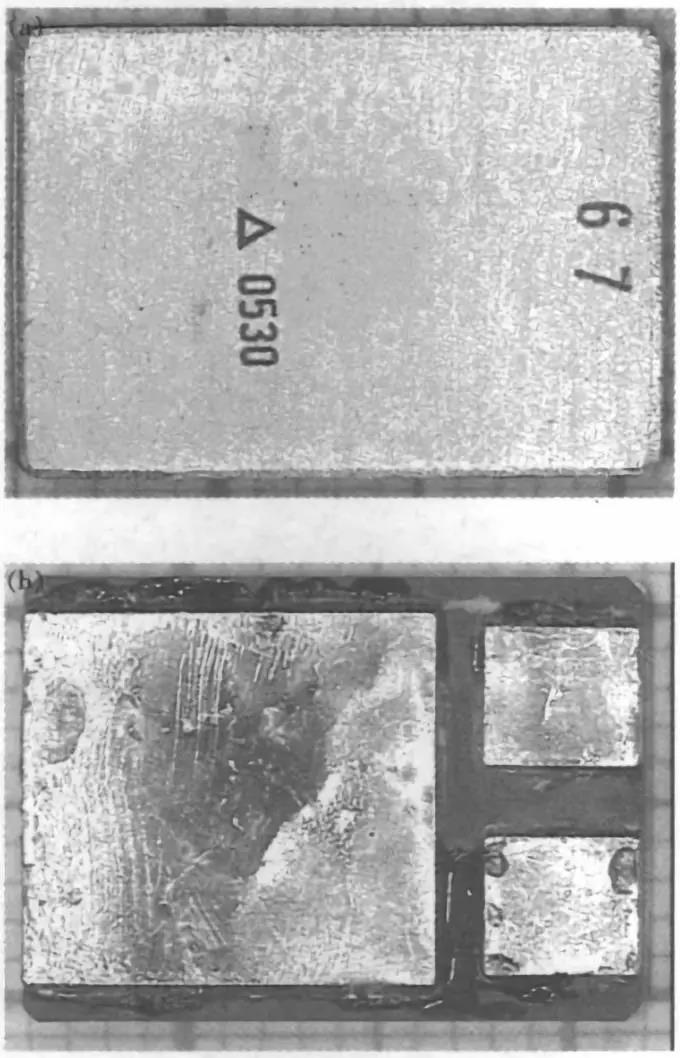

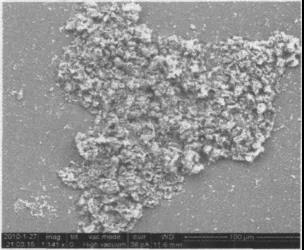

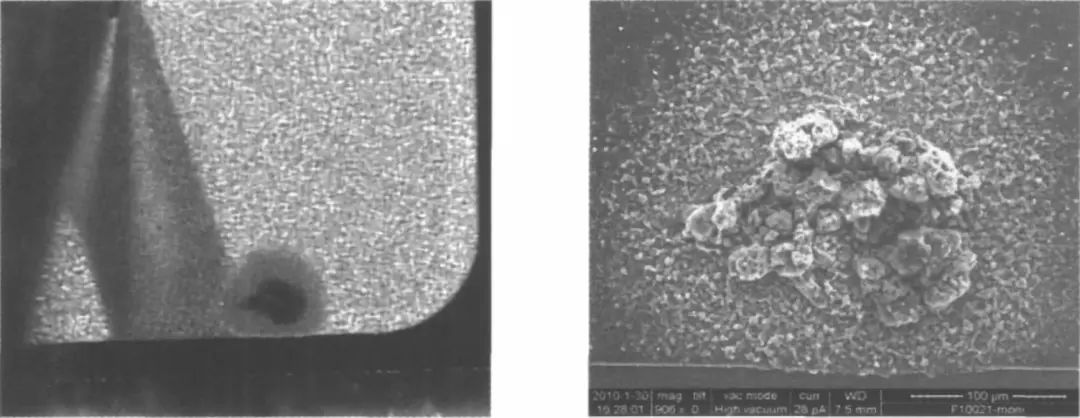

用机械法开帽,用体式和扫描电子显微镜对器件内部进行检查,发现短路二极管内部芯片表面存在黑色的异常点,异常点外围为Al金属电极受热皱起的形貌,中间为半导体和金属共融的形貌,异常点形貌有别于常见的过电应力导致的烧毁点形貌(图3)。

图3 短路二极管表面异常点

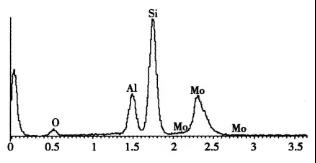

用扫描电镜和能谱仪对器件芯片进行检查和分析,发现异常点的成分主要为Si、Al、Mo、O(图4),分析认为该处发生了硅铝共熔,判断该点为芯片短路点。对芯片表面的其他区域进行能谱分析,其成分为Al对芯片表面的Al金属电极以及金属Mo进行腐蚀,发现金属和半导体的共融物质仍然存在,能谱分析发现异常点仍然含有Si、Al、Mo、O,腐蚀掉Al和Mo后的异常点形貌见图5。

图4 图3b方框位置能谱分析谱图

图5 腐蚀掉Al和Mo后的异常点形貌

2. 分析与讨论

2.1 肖特基二极管的制作过程

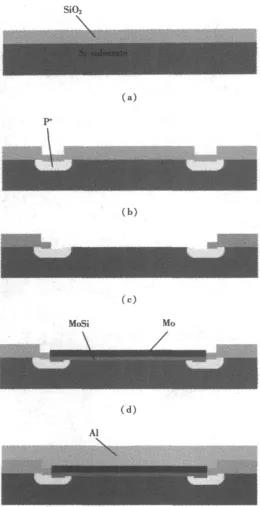

肖特基接触的制造通常是将合适的金属蒸发在N+-N外延结构的表面上来完成的。对于高耐压肖特基二极管,通常采用边缘终端技术(扩散P+保护环)来改善其边缘电场的集成从而提高其反向击穿电压。目前主流的肖特基二极管(几十V至200V以上)工艺流程见图6。图6a~图6e的工艺流程分别为在N+/N衬底上热氧化生长SiO2作P+扩散的掩蔽层;先后进行光刻、刻蚀、B注入、推结,形成器件结终端;刻蚀SiO2形成肖特基势垒区(即有源区);溅射/蒸发Mo金属,继续退火处理,形成MoSi2金属势垒;蒸发铝,形成电极。

2.2 失效机理分析

从能谱分析可以看出,异常点处除了存在上述的Al、Mo、Si外,还有O。O有2个可能的来源,一是封装内部的O2,二是器件制作过程SiO2残留。器件封装内部含有少量O2,烧毁点在过热过程中发生局部氧化,在异常点处可分析出O,而内部气氛分析表明器件密封腔里不含有O2,因此可排除这种来源;结合肖特基器件工艺流程,判断O来源于氧化层刻蚀过程(图6c)中残留的少量或极少量SiO2。

图6 主流的肖特基二极管工艺流程

残留的SiO2经后续金属淀积、合金工艺处理后,相当于在肖特基二极管上并联了一个MOS电容(图7),而MOS电容是ESD敏感器件,这也解释了为什么该器件标识的抗静电能力为一级(1个Δ),器件失效点含有O,表明失效点即为残留SiO2的位置。

图7 有SiO2残留时肖特基二极管等效电路图

失效点首先发生介质击穿,接着引发大电流,从而发生了半导体和金属的局部共融。导致残留介质击穿的机理有2个,一个是与时间相关的介质击穿(TDDB),另一个则是静电损伤。

TDDB的典型时间-失效分布属于对数正态分布,时间超过100h以后,失效率明显下降,调查该次失效的背景信息,该器件在失效前累计工作时间为1455h,且器件出厂前进行了240h的高温反偏试验,排除器件残留SiO2位置发生经时击穿的可能性。

通过上述分析,判断静电放电导致残留SiO2的位置发生介质击穿,击穿后引发的电流导致半导体和金属的局部共融。

2.3 验证试验

取同批次良品1只,依据GJB548B-2005方法3015对器件进行静电放电试验,试验后用TEK370晶体管图示仪测试器件引脚Pin1-Pin3的I-V特性,发现器件反向漏电变大。模拟器件工作状态给器件持续加电4h,观察器件I-V特性,漏电有逐渐变大的趋势,接近短路。

对模拟样品开帽进行内部目检,发现施加应力的二极管管芯存在类似于失效器件的黑色硅铝共熔点,能谱分析该点的成分为Si、Al、Mo、O与失效器件失效点相同(图8)。

图8 模拟试验样品失效点形貌

3. 结论

1)由于高耐压肖特基整流管通常利用扩散P+保护环的方法改善其反向耐压,需要在N+/N衬底上热氧化生长SiO2作P+扩散的掩蔽层,而在刻蚀SiO2形成肖特基势垒区时,往往会由于各种原因(例如Si表面的微缺陷、刻蚀不干净等)残留少量或极少量的SiO2,从而在肖特基二极管中引入对ESD敏感的MOS电容结构,造成器件的抗静电能力大幅下降,若使用中静电防护措施不当,很容易对器件造成静电损伤。

2)肖特基整流管生产厂家在刻蚀SiO2的工艺过程中应特别注意将SiO2刻蚀干净;针对这类器件,在生产、试验、运输和使用中要按照一类静电敏感器件进行静电防护,在失效分析时也应考虑静电损伤这一失效机理。